HUAWEI Compatible QSFP-100G-PSM4 Quick Spec:

Part #: QSFP-100G-PSM4 QSFP-100G-PSM4-EXT

Form Factor: QSFP28

TX Wavelength: 1310nm

Reach: 2km

Cable Type: SMF

Rate Category: 100GBase

Interface Type: PSM4

DDM: Yes

Connector Type: MPO Optical Power Budget: 11 dB

TX Power Min/Max: +2.0 to +4.5 dBm RX Power Min/Max: -9.0 to +4.5 dBm

HUAWEI Compatible QSFP-100G-PSM4 Features:

QSFP28 MSA form factor

Compliant to IEEE 802.3bm 100GBASE PSM4 4 independent full-duplex channels

Up to 2km reach for G.652 SMF

Single +3.3V power supply

Operating Case Temperature

Standard 0 to +70 °C

Extended -4 to +85 °C

Industrial -40 to +85 °C

Maximum power consumption 3.5W

HUAWEI Compatible QSFP-100G-PSM4 Applications:

100G Ethernet Links

Infiniband QDR and DDR interconnects

Datacenter and Enterprise networking

HUAWEI Compatible QSFP-100G-PSM4 Overview

The QSFP-100G-PSM4 is a parallel 100 Gbps single mode optical transceiver designed for optical communication applications. This product provides increased port density, offering four independent transmit and receive channels. Each channel operates at 25Gbps, resulting in an aggregate data rate of 100Gbps on 2km of single mode fiber. An optical fiber ribbon cable with an MTP/MPO connector can be plugged into the QSFP28 module receptacle. The guide pins inside the receptacle ensure proper alignment. The product is designed with form factor, optical/electrical connection and digital diagnostic interface according to the QSFP28 Multi- Source Agreement (MSA). It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference. The module can be managed through the I2C two-wire serial interface. The product is designed with form factor, optical/electrical connection and digital diagnostic interface according to the QSFP28 Multi-Source Agreement (MSA). It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference. The module can be managed through the I2C two-wire serial interface.

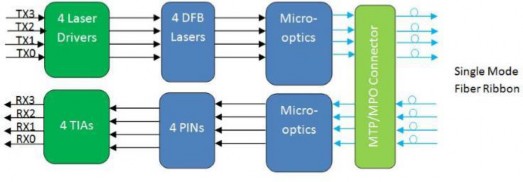

HUAWEI Compatible QSFP-100G-PSM4 Functional Diagram

This product is a QSFP28 parallel single mode optical transceiver with an MTP/MPO fiber ribbon connector. The transmitter module accepts electrical input signals compatible with Common Mode Logic (CML) levels. All input data signals are differential and internally terminated. The receiver module converts parallel optical input signals via a photo detector array into parallel electrical output signals. The receiver module outputs electrical signals are also voltage compatible with Common Mode Logic (CML) levels. All data signals are differential and support a data rates up to 25Gb/s per channel. Figure 1 shows the functional block diagram of this product.

Figure 1. Functional diagram

A single +3.3V power supply is required to power up the module. Both power supply pins VccTx and VccRx are internally connected and should be applied concurrently. Per MSA the module offers 7 low speed hardware control pins (including the 2-wire serial interface): ModSelL, SCL, SDA, ResetL, LPMode, ModPrsLand IntL. Module Select (ModSelL) is an input pin. When held low by the host, the module responds to 2-wire serial communication commands. The ModSelL allows the use of multiple QSFP28 modules on a single 2-wire interfacebus –individual ModSelL lines for each QSFP28 module must be used. Serial Clock (SCL) and Serial Data (SDA) are required for the 2-wire serial bus communication interface and enable the host to access the QSFP28 memory map. The ResetL pin enables a complete module reset, returning module settings to their default state, when a low level on the ResetL pin is held for longer than the minimum pulse length. During the execution of a reset the host shall disregard all status bits until the module indicates a completion of the reset interrupt. The module indicates this by posting an IntL (Interrupt) signal with the Data_Not_Ready bit negated in the memory map. Note that on power up (including hot insertion) the module should post this completion of reset interrupt without requiring are set. Low Power Mode (LPMode) pin is used to set the maximum power consumption for the module in order to protect hosts that are not capable of cooling higher power modules, should such modules be accidentally inserted. Module Present (ModPrsL) is a signal local to the host board which, in the absence of a module, is normally pulled up to the host Vcc. When a module is inserted into the connector, it completes the path to ground through a resistor on the host board and asserts the signal. ModPrsL then indicates a module is present by setting ModPrsLto a“Low” state. Interrupt (IntL) is an output pin. Low indicates a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt using the 2-wire serial interface. The IntL pin is an open collector output and must be pulled to the Host Vcc voltage on the Host board. This transceiver is specified as ESD threshold 1KV for high speed data pins and 2KV for all others electrical input pins, tested per MIL- STD-883, Method 3015.4 /JESD22-A114-A (HBM). However, normal ESD precautions are still required during the handling of this module. This transceiver is shipped in ESD protective packaging. It should be removed from the packaging and handled only in an ESD protected environment. This is a Class 1 Laser Product according to IEC 60825-1:2007. This product complies with 21 CFR 1040.10 and 1040.11 except for deviations pursuant to Laser Notice No. 50.

Parameter | Symbol | Min | Max | Unit |

Storage Temperature | Ts | -40 | +85 | °C |

Operating Case Temp (Standard) | TOP | 0 | 70 | °C |

Operating Case Temp (Industrial) | TOP | -40 | 85 | °C |

Power Supply Voltage | Vcc | -0.5 | 3.6 | V |

Relative Humidity (non- condensation) | RH | 5 | 85 | % |

Damage threshold, each lane | THd | 4.5 | dBm |

HUAWEI Compatible QSFP-100G-PSM4 Specifications Absolute Maximum Ratings

Recommended Operating Conditions

Parameter | Symbol | Min | Typ | Max | Unit |

Power Supply Voltage | Vcc | 3.135 | 3.3 | 3.465 | V |

Data Rate, each Lane | 25.78125 | Gb/s | |||

Control Input Voltage High) | 2 | Vcc | V | ||

Control Input Voltage Low | 0 | 0.8 | V | ||

Link Distance (SM fiber) | D | 0.002 | 2 | km |

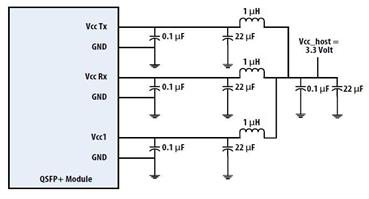

Recommended Power Supply Filter

Electrical Characteristics

Parameter | Symbol | Min | Typ | Max | Unit |

Power Consumption | - | 3.5 | W | ||

Supply Current | Icc | 1.1 | A | ||

Transceiver power-on initialization time (note1) | 2000 | ms |

Electrical Characteristics-Transmitter (each lane)

Parameter | Symbol | Min | Typ | Max | Unit |

Single-ended input voltage tolerance (note 2) | -0.3 | 4.0 | V | ||

AC common mode input voltage tolerance | 15 | mV | |||

Differential input voltage swing threshold | 50 | mVpp | |||

Differential input voltage swing | Vin.pp | 190 | 700 | mVpp | |

Differential input impedance | Zin | 90 | 100 | 110 | Ω |

Electrical Characteristics-Receiver

Parameter | Symbol | Min | Typ | Max | Unit |

Single-ended output voltage | -0.3 | 4.0 | V | ||

AC common mode output voltage | 7.5 | mV | |||

Differential output voltage swing | Vout.pp | 300 | 850 | mVpp | |

Differential output impedance | Zout | 90 | 100 | 110 | ohm |

Notes:

Power-on Initialization Time is the time from when the power supply voltages reach and remain above the minimum recommended operating supply voltages to the time when the module is fully functional.

The single ended input voltage tolerance is the allowable range of the instantaneous input signals.

Optical Characteristics-Transmitter

Parameter | Symbol | Min | Typ | Max | Unit |

Center wavelength | λc | 1260 | 1310 | 1355 | nm |

Side Mode Suppression Ratio | SMSR | 30 | dB | ||

Total average launch power | PT | 9.5 | dBm | ||

Average launch power, each lane | PAVG | 1.0 | 3.5 | dBm | |

Optical Modulation Amplitude(OMA), each lane (Note ) | POMA | 2.0 | 4.5 | dBm | |

Difference in launch power between any two lanes | Ptx,diff | 5 | dB | ||

Launch power in OMA minus Transmitter and Dispersion Penalty (TDP), each Lane | 1.0 | dBm | |||

TDP, each lane | TDP | 3.2 | dB | ||

Extinction Ratio | ER | 3.5 | dB | ||

Relative Intensity Noise | RIN | -128 | dB/Hz | ||

Optical return loss Tolerance | TOL | 12 | dB | ||

Transmitter reflectance | RT | -12 | dB | ||

Average Launch Power OFF Transmitter, each Lane | Poff | -30 | dBm | ||

Transmitter Eye Mask Definition {X1, X2, X3, Y1, Y2, Y3} | {0.25, 0.4, 0.45, | 0.25, 0.28, 0.4} |

Note: Even if the TDP < 1 dB, the OMA min must exceed the minimum value specified here.

Optical Characteristics-Receiver

Parameter | Symbol | Min | Typ | Max | Unit |

Center wavelength | λc | 1260 | 1310 | 1355 | nm |

Damage threshold, each lane (note ) | THd | 4.5 | dB | ||

Average receive power, each lane | -9.0 | 3.5 | dBm | ||

Receiver reflectance | RR | -12 | dBm | ||

Receiver power (OMA), each lane | 4.5 | dBm | |||

Receiver sensitivity (OMA), each lane | SEN | -9.0 | dB | ||

Difference in receive power between any two lanes (OMA) | Prx,diff | 5.5 | dBm | ||

LOS Assert | LOSA | -18 | dB | ||

LOS Deassert | LOSD | -15 | dB | ||

LOS Hysteresis | LOSH | 0.5 | dB/Hz | ||

Receiver Electrical 3dB upper Cutoff Frequency, each Lane | Fc | 31 | dB |

Note: The receiver shall be able to tolerate, without damage, continuous exposure to a modulated optical input signal having this power level on one lane. The receiver does not have to operate correctly at this input power.

Digital Diagnostic Functions

The following digital diagnostic characteristics are defined over the normal operating conditions unless otherwise specified.

Parameter | Symbol | Min | Typ | Max | Unit | Notes |

Temperature monitor absolute error | DMITEMP | -3 | 3 | deg. C | Over operating temperature range | |

Supply voltage monitor absolute error | DMIVCC | -0.1 | 0.1 | V | Over Full operating range | |

Channel RX power monitor absolute error | DMIRX_CH | -2 | 2 | dB | 1 | |

Channel Bias current monitor | DMIIbias_CH | -10% | 10% | mA | ||

Channel TX power monitor absolute error | DMITX_CH | -2 | 2 | dB | 1 |

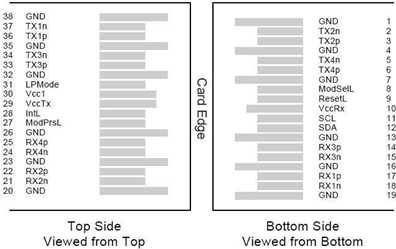

PIN Assignment and Function Definitions

PIN Definition

PIN | Signal Name | Description |

1 | GND | Ground (1) |

2 | Tx2n | CML-I Transmitter 2 Inverted Data Input |

3 | Tx2p | CML-I Transmitter 2 Non-Inverted Data Input |

4 | GND | Ground (1) |

5 | Tx4n | CML-I Transmitter 4 Inverted Data Input |

6 | Tx4p | CML-I Transmitter 4 Non-Inverted Data Input |

7 | GND | Ground (1) |

8 | ModSelL | LVTLL-I Module Select |

9 | ResetL | LVTLL-I Module Reset |

10 | VCCRx | +3.3V Power Supply Receiver (2) |

11 | SCL | LVCMOS-I/O 2-Wire Serial Interface Clock |

12 | SDA | LVCMOS-I/O 2-Wire Serial Interface Data |

13 | GND | Ground (1) |

14 | Rx3p | CML-O Receiver 3 Non-Inverted Data Output |

15 | Rx3n | CML-O Receiver 3 Inverted Data Output |

16 | GND | Ground (1) |

17 | Rx1p | CML-O Receiver 1 Non-Inverted Data Output |

18 | Rx1n | CML-O Receiver 1 Inverted Data Output |

19 | GND | Ground (1) |

20 | GND | Ground (1) |

21 | Rx2n | CML-O Receiver 2 Inverted Data Output |

22 | Rx2p | CML-O Receiver 2 Non-Inverted Data Output |

23 | GND | Ground (1) |

24 | Rx4n | CML-O Receiver 4 Inverted Data Output |

25 | Rx4p | CML-O Receiver 4 Non-Inverted Data Output |

26 | GND | Ground (1) |

27 | ModPrsL | Module Present |

28 | IntL | Interrupt |

29 | VCCTx | +3.3V Power Supply Transmitter (2) |

30 | VCC1 | +3.3V Power Supply |

31 | LPMode | LVTLL-I Low Power Mode |

32 | GND | Ground (1) |

33 | Tx3p | CML-I Transmitter 3 Non-Inverted Data Input |

34 | Tx3n | CML-I Transmitter 3 Inverted Data Input |

35 | GND | Ground (1) |

36 | Tx1p | CML-I Transmitter 1 Non-Inverted Data Input |

37 | Tx1n | CML-I Transmitter 1 Inverted Data Input |

38 | GND | Ground (1) |

Notes:

All Ground (GND) are common within the QSFP+ module and all module voltages are referenced to this potential unless noted otherwise. Connect these directly to the host board signal common ground plane.

VccRx, Vcc1 and VccTx are the receiving and transmission power suppliers and shall be applied concurrently. The connector pins are each rated for a maximum current of 500mA.

Licensing

The following U.S. patents are licensed by Finisar to FluxLight, Inc.:

U.S. Patent Nos: 7,184,668, 7,079,775, 6,957,021, 7,058,310, 6,952,531, 7,162,160, 7,050,720